�·���O(sh��)Ӌ��һ�(xi��ng)�P(gu��n)�I���ֺĕr���΄�(w��)����������F(xi��n)�κΆ��}����Ҫ���̎������W(w��ng)�j(lu��)����Ԫ���ؙz�������O(sh��)Ӌ��������f�·���O(sh��)ӋҪ��ļ�(x��)�ij̶Ȳ�����оƬ�O(sh��)Ӌ�������

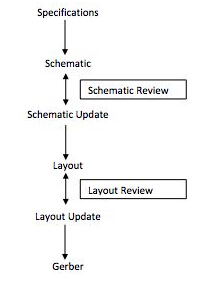

���͵��·���O(sh��)Ӌ���������²��E�M�ɣ�

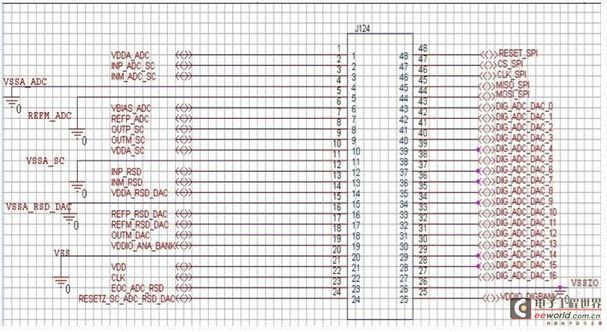

ǰ���������E���ĕr�g��࣬��?y��n)�ԭ��D�z����һ���ֹ��^������������һ������1000�l���������B����SoC�·�塣�˹��z��ÿһ���B�������L��ζ��һ�(xi��ng)�΄�(w��)��������(sh��)�ϣ��z��ÿ���B�����Dz����ܵ��������������(d��o)����K�·������}�������e�`���B���������Ҹ���(ji��)�c(di��n)�ȡ�

ԭ��D���@�A��һ������R������}��

�� �����e�`������APLLVDD��APLL_VDD

�� �������}������VDDE��vdde

�� ƴ���e�`

�� ��̖��·���}

�� ����߀���S��

���˱����@Щ�e�`���������(y��ng)ԓ�зN�����܉��ڎ���ĕr�g��(n��i)�z��������ԭ��D���@������������ԭ��D����팍(sh��)�F(xi��n)���������ԭ��D������Ŀǰ���·���O(sh��)Ӌ������߀����Ҋ������ͨ�^ԭ��D���������Ҫ��Ĺ�(ji��)�c(di��n)�^����Kݔ���Y(ji��)�������������Ԅәz�������B�ӆ��}��

����ͨ�^һ���(xi��ng)Ŀ��(sh��)���M(j��n)�н�����������������]�·���һ�����Ϳ�D��

�ڏ�(f��)�s���·���O(sh��)Ӌ������B����(sh��)�������_(d��)����(sh��)ǧ�l���������O�����ĸ��ĺܿ������M(f��i)�S���r�gȥ�z�顣

ԭ��D���治�H�ܹ�(ji��)ʡ�O(sh��)Ӌ�r�g�����������������·���|(zh��)������������������̵�Ч��������

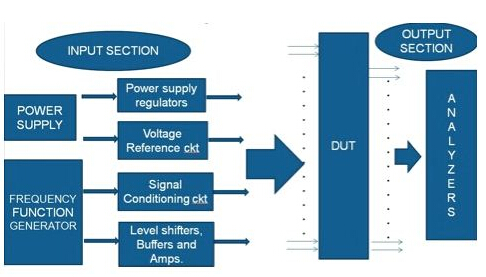

һ�����͵Ĵ��y�O(sh��)��(DUT)��������һЩ��̖��

���y�O(sh��)���ڽ�(j��ng)�^ijЩ�A(y��)�{(di��o)������и��N���ӵ���̖�������и��Nģ�K������緀(w��n)���������\(y��n)�ŵ�����������̖�{(di��o)���������������]ͨ�^��(w��n)�����õ���һ�������̖���ӣ�

���y�O(sh��)���ڽ�(j��ng)�^ijЩ�A(y��)�{(di��o)������и��N���ӵ���̖�������и��Nģ�K������緀(w��n)���������\(y��n)�ŵ�����������̖�{(di��o)���������������]ͨ�^��(w��n)�����õ���һ�������̖���ӣ�

�����(y��n)�C�B���P(gu��n)ϵ����(zh��)�����w�z�飬ʹ����ԭ��D��������ԭ��D������ԭ��D��(chu��ng)���������yԇƽ�_��(chu��ng)���ͷ���M�������

�ڜyԇƽ�_��(chu��ng)���^���У����м�����̖�o����Ҫ��ݔ�������Ȼ���ڸ��dȤ����̖�c(di��n)�^��ݔ���Y(ji��)������

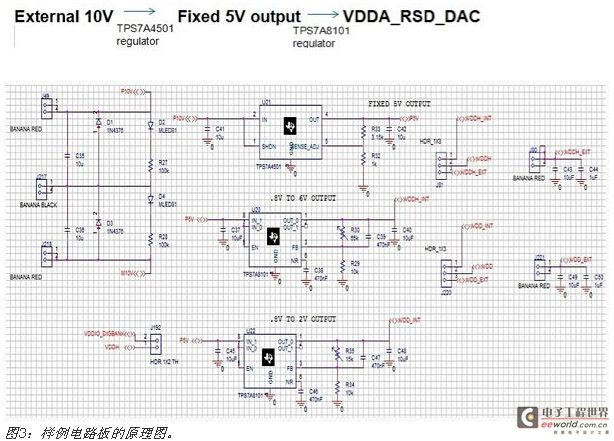

����ͨ�^��̽��B�ӵ����^�칝(ji��)�c(di��n)��(sh��)�F(xi��n)�����^�����������(ji��)�c(di��n)늉��Ͳ��ο���ָʾԭ��D�Л]���e�`������������̖�B�Ӷ����õ��Ԅәz�顣

�҂���һ�������@���D��һ���ֲ�����������̽�y�Ĺ�(ji��)�c(di��n)��늉�������Ҋ��

����ڷ���Ď�������������҂�����ֱ���^��Y(ji��)������_�J(r��n)�·��ԭ��D�Ƿ����_����������ͨ�^�м�(x��)�{(di��o)��(ji��)������̖��Ԫ��ֵ߀���Ԍ�(sh��)�F(xi��n)�O(sh��)Ӌ���ĵ��{(di��o)�顣���ԭ��D������Թ�(ji��)ʡ�·���O(sh��)Ӌ�͙z���ˆT�Ĵ����r�g���������������O(sh��)Ӌ���_�ԵęC(j��)����